元件充电模式(CDM) ESD被认为是代表ESD充电和快速放电的首要实际ESD模型,能够恰如其分地表示当今集成电路(IC)制造和装配中使用的自动处理设备所发生的情况。到目前为止,在制造环境下的器件处理过程中,IC的ESD损害的 大原因是来自充电器件事件,这一点已广为人知。1

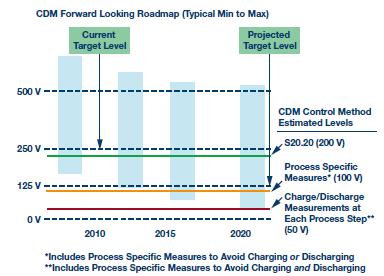

充电器件模型路线图

对IC中更高速IO的不断增长的需求,以及单个封装中集成更多功能的需要,推动封装尺寸变大,因而维持JEP1572, 3中讨论的推荐目标CDM级别将是一个挑战。还应注意,虽然技术扩展对目标级别可能没有直接影响(至少低至14 nm),但这些 技术改进了晶体管性能,进而也能支持更高IO性能(传输速率),因此对IO设计人员而言,实现当前目标级别同样变得很困难。由于不同测试仪的充电电阻不一致,已公布的ESD协会(ESDA)截止20204年路线图建议,CDM目标级别将需要再次降低,如图1所示。

图1.2010年及以后的充电器件模型灵敏度限值预测(版权所有 2016 EOS/ESD协会)

快速浏览图1不会发现CDM目标级别有明显变化,但进一步查阅ESDA提供的数据(如图2所示)可知,CDM ESD目标级别的分布预期会有重大变化。

图2.充电器件模型灵敏度分布组别前瞻(版权所有 2016 EOS/ESD协会)

为何讨论此变化很重要?它指出了需要采用一致的方法来测试整个电子行业的CDM,应排除多种测试标准所带来的一些不一致性。现在,确保制造业针对ESDA讨论的CDM路线图做好适当准备比以往任何时候都更重要。这种准备的一个关键方面是确保制造业从各半导体制造商收到的关于器件CDM鲁棒性水平的数据是一致的。对一个协调一致的CDM标准的需求从来没有像现在这样强烈。再加上持续不断的技术进步,IO性能也会得到提高。这种对更高IO性能的需要(以及降低引脚电容的需要),迫使IC设计人员别无选择,只能降低目标级别,进而需要更精密的测量(在ANSI/ESDA/JEDEC JS-002中有说明)。

新联合标准

在ANSI/ESDA/JEDEC JS-002之前有四种现存标准:传统的JEDEC (JESD22-C101)5、ESDA S5.3.16、AEC Q100-0117和EIAJ ED-4701/300-2标准8。ANSI/ESDA/JEDEC JS-002(充电器件模型、器件级别)9代表了将这四种现有标准统一为单一标准的重大努力。虽然所有这些标准都产生了有价值的信息,但多种标准的存在对行业不是好事。不同方法常常产生不同的通过级别,多种标准的存在要求制造商支持不同的测试方法,而有意义的信息并无增加。因此,以下两点非常重要:IC充电器件抑制能力的单一测量水平是广为人知的,以确保CDM ESD设计策略得到正确实施;IC的充电器件抑制能力同它将接触到的制造环境中的ESD控制水平一致。

为了解决这个问题,2009年成立的ESDA和JEDEC CDM联合工作小组(JWG)开发了JS-002。此外,JWG希望根据引入场感应CDM (FICDM)以来所获得的经验教训对FICDM进行技术改进10。 ,JWG希望尽量减少对电子行业的冲击。为了减少行业冲击,工作小组决定,联合标准不应要求购买全新场感应CDM测试仪,并且通过/失败水平应尽可能与JEDEC CDM标准一致。JEDEC标准是使用 广泛的CDM标准,因此JS-002与当前制造业对CDM的理解保持一致。

虽然JEDEC和ESDA的测试方法非常相似,但两种标准之间有一些不同之处需要化解。JS-002还试图解决一些技术问题。一些 重要问题列示如下。

标准之间的差异

场板电介质厚度

用于验证系统的验证模块

示波器带宽要求

波形验证参数

标准的技术问题

测量带宽要求对CDM而言太慢

人为地让JEDEC标准中的脉冲宽度很宽

为了达成目标并实现统一,作出了如下硬件和测量选择。在为期五年的文件编制过程中,工作小组进行了大量测量才作出这些决定。

硬件选择

使用JEDEC电介质厚度

使用JEDEC“硬币”进行波形验证

禁止在放电路径中使用铁氧体

测量选择

系统验证/验收需要 6 GHz带宽的示波器

例行系统验证允许使用1 GHz示波器

尽量减少数据损坏并讨论隐藏电压调整

让目标峰值电流与现有JEDEC标准一致

指定与JEDEC压力级别匹配的测试条件;对于JS-002测试结果,指的是测试条件(TC);对于JEDEC和AEC,指的是伏特(V)

对于JS-002,调整场板电压以提供与传统JEDEC峰值电流要求对应的正确峰值电流

确保较大封装完全充电

为确保较大封装完全充电,引入了一个新的程序

下面说明这些改进。

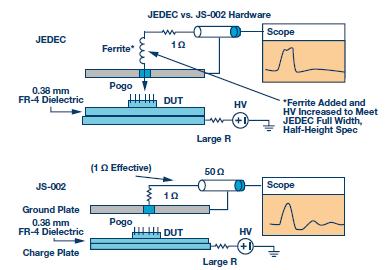

JS-002硬件选择

JS-002 CDM硬件平台代表了ESDA S5.3.1探针组件或测试头放电探针同JEDEC JESD22-C101验证模块和场板电介质的结合。图3所示为硬件对比。ESDA探针组件的放电路径中没有特定铁氧体。FICDM测试仪制造商认为,铁氧体是必要的,增加铁氧体可提高500 ps的半峰全宽(FWHH)额定 值,并将Ip2(第二波峰)降至 波峰Ip1的50%以下,从而满足传统JEDEC要求。JS-002去掉了此铁氧体,从而消除了放电中的这种限制因素,使得放电波形更准确,高带宽示波器在Ip1时看到的振铃现象不再存在。

图3.JEDEC和JS-002平台硬件原理图

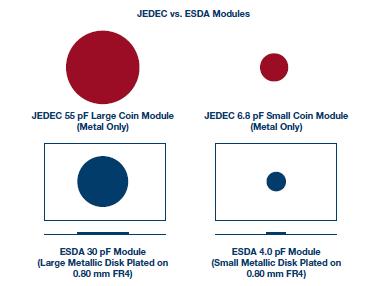

图4显示了ESDA和JEDEC CDM标准验证模块的区别。ESDA标准提供两个电介质厚度选项,并结合验证模块(第二个选项是模块和场板之间有一层 多130 μm的额外塑料薄膜,用于测试带金属封装盖的器件)。JEDEC验证模块/FR4电介质代表一个单一小/大验证模块和电介质选项,支持它的JEDEC标准用户要多得多。

图4.ESDA和JEDEC验证模块比较JS-002使用JEDEC模块。

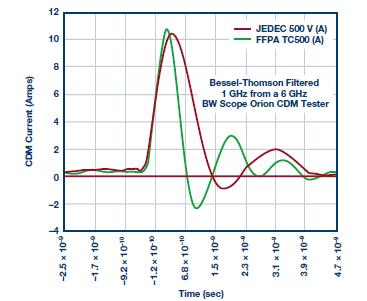

JS-002测量选择

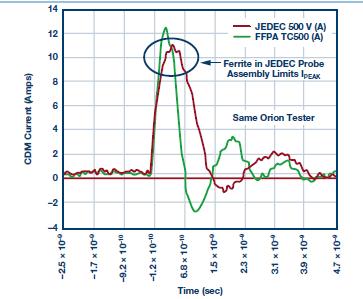

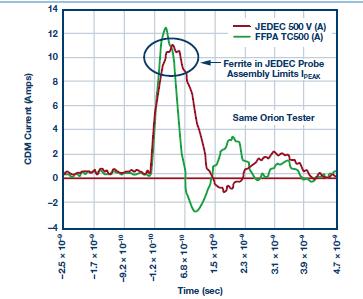

在JS-002标准制定的数据收集阶段,CDM JWG发现需要更高带宽的示波器才能 测量CDM波形。1 GHz带宽示波器未能捕捉到真正的 峰值。图5和图6说明了这一点。

图5.大JEDEC验证模块在500 V JEDEC时与JS-002 TC500在1 GHz时的CDM波形

图6.大JEDEC验证模块在500 V JEDEC时与JS-002 TC500在6 GHz时的CDM波形

例行波形检查,例如每日或每周的检查,仍可利用1 GHz带宽示波器进行。然而,对不同实验室测试站点的分析表明,高带宽示波器能提供更好的站点间相关性。11例行检查和季度检查推荐使用高带宽示波器。年度验证或更换/修理测试仪硬件之后的验证需要高带宽示波器。

表1.JS-002波形数据记录表示例,显示了造成TC(测试条件)电压的因素9

测试仪—系统#1

极性 = 正

示波器带宽 = 8 GHz

因子/失调 终设置 = 0.82

模块大小

日期

%RH

测试条件

软件电压

IP AVG (A)

T R AVG

TD AVG

IP2 AVG

IP2 (% IP1)

大

日/月/年

X%

TC 500

500

12.1

275

610

4.3

36%

小

日/月/年

X%

TC 500

500

7.30

185

400

3.7

51%

大

日/月/年

X%

TC 125

125

2.90

283

611

1.1

38%

小

日/月/年

X%

TC 125

125

1.90

201

395

1.1

58%

大

日/月/年

X%

TC 250

250

6.00

276

609

2.2

37%

小

日/月/年

X%

TC 250

250

3.70

186

397

2.1

57%

大

日/月/年

X%

TC 750

750

18.30

274

611

7.2

39%

小

日/月/年

X%

TC 750

750

11.0

190

398

6.1

55%

大

日/月/年

X%

TC 1000

1000

24.40

276

612

9.2

38%

小

日/月/年

X%

TC 1000

1000

14.60

187

399

7.4

51%

测试仪CDM电压设置

CDM JWG同时发现,对于不同测试仪平台,为了获得符合先前ESDA和JEDEC标准的标准测试波形,实际板电压设置需要有相当大的差异(例如,特定电压设置为100 V或更大)。这在任何标准中都没有说明。JS-002 地确定了将 峰值电流(以及测试条件所代表的电压)缩放到JEDEC峰值电流水平所需的偏移或因数。JS-002附录G对此有详细说明。表1显示了一个包含此特性的验证数据实例。

在设定测试条件下确保超大器件完全充电

在JS-002开发的数据收集阶段还发现了一个与测试仪相关的问题:放电之前,某些测试系统未将大验证模块或器件完全充电到设定电压。不同测试系统的大值场板充电电阻(位于充电电源和场板之间的串联电阻)不一致,影响到场板电压完全充电所需的延迟时间。结果,不同测试仪的 峰值放电电流可能不同,影响CDM的通过/失败分类,尤其是大器件。

因此,工作小组撰写了详实的附录H(“确定适当的充电延迟时间以确保大模块或器件完全充电”),描述了用于确定器件完全充电所需延迟时间的程序。当出现峰值电流饱和点(Ip基本保持稳定,设置更长的延迟时间也不会使它改变)时,说明达到了适当的充电延迟时间,如图7所示。确定此延迟时间,确保放电之前,超大器件能够完全充电到设定的测试条件。

图7.峰值电流与充电时间延迟关系图示例,显示了饱和点/充电时间延迟9

电子行业逐步采用JS-002

对于采用ESDA S5.3.1 CDM标准的公司,JS-002标准取代了S5.3.1,应将S5.3.1废弃。对于先前使用JESD22-C101的公司,JEDEC可靠性测试规范文件JESD47(规定JEDEC电子元件的所有可靠性测试方法) 近进行了更新,要求用JS-002代替JESD22-C101(2016年末)。JEDEC会员公司转换到JS-002的过渡时期现已开始。很多公司(包括ADI和Intel)已经对所有新产品利用JS-002标准进行测试。

国际电工委员会(IEC) 近批准并更新了其CDM测试标准IS 60749-2812。此标准全盘纳入JS-002作为其指定测试标准。

汽车电子理事会(AEC)目前有一个CDM小组委员会,其正在更新Q100-011(集成电路)和Q101-005(无源器件)车用器件CDM标准文件以纳入JS-002,并结合AEC规定的测试使用条件。这些工作预计会在2017年底完成并获批准。

结语

观察ESDA提供的CDM ESD路线图,可知在更高IO性能的驱动下,CDM目标级别会继续降低。制造业对器件级CDM ESD耐受电压的认知比以往任何时候都更重要,而来自不同CDM ESD标准的不一致产品CDM结果是无法传达这一讯息的。ANSI/ESDA/JEDEC JS-002有机会成为 个真正的适用于全行业的CDM测试标准。消除CDM测试头放电路径中的电容,可显著改善放电波形的质量。引入高带宽示波器用于验证,提高到五个测试条件波形验证级别,以及保证适当的充电延迟时间——所有这些措施显著降低了不同实验室的测试结果差异,改善了站点间的可重复性。这对确保向制造业提供一致的数据至关重要。电子行业接受JS-002标准之后,将有能力更好地应对前方的ESD控制挑战。

联系人:徐经理

手机:13907330718

电话:0731-22222718

邮箱:hniatcom@163.com

地址: 湖南省株洲市石峰区联诚路79号轨道智谷2号倒班房6楼603室